GOSSAMER, or “Gigascale Oriented Solid State flAsh Memory for EuRope” is a European Integrated ICT project carried out by a consortium of 13 partners and supported by the European Commission through the FP7 program.

The GOSSAMER project aims at the development of the technology for very high density Non Volatile Memories for mass storage applications down to the 22 nm technology node.

During the last 15 years, ICTs have provided a number of radically new devices / techno-toys that have improved the daily life of the EU citizen: mobile phone, digital camera, MP3 players, PC, PDA, credit cards, video on discs, flat screen, HD TV, fast communications (ADSL) .

The need of more and more “memory” is shared by all applications of ICTs such as enhancing life comfort and security, leisure, education, business and improving work productivity.

At the moment there seems to be no sign for a slowing down of memory requirements: in spite of the doubling of memory density every 18 months, the diffusion of broadband communication and digital appliances, and the constant demand for better quality of images and sound, is creating an ever increasing need for large memories in a variety of new media.

Solid-state memories are the preferred solution for mobile applications. Their main advantages are the use of consolidated technology, the lack of any mechanical,parts, which results in stronger ruggedness, lighter weight, smaller form-factor, better reliability and, above all, lower power dissipation.

Main Objectives:

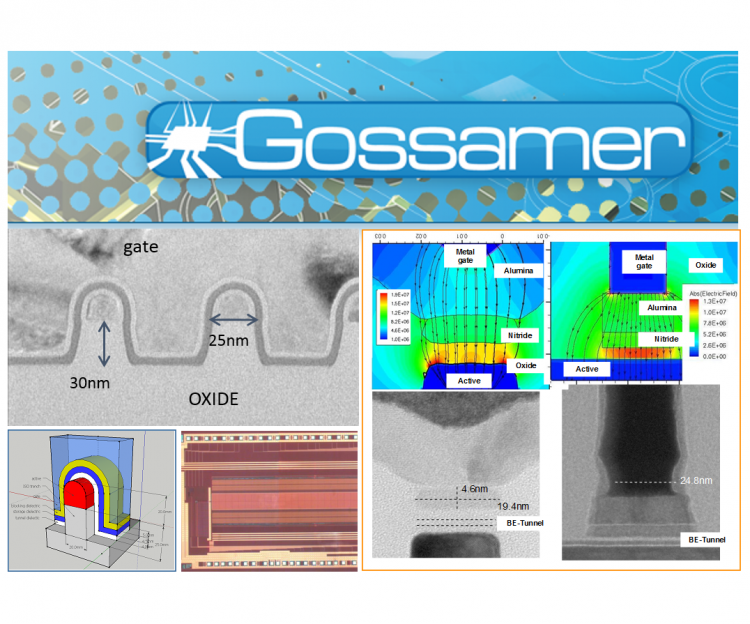

The project addresses for the first time the development of large size NAND Flash memories based on the charge trapping mechanism, instead of the conventional floating gate concept, for technology generations in the range of 36-28nm.

The project was started in 2008 with the target to develop a NAND Flash memory technology for mass storage based on the charge trapping mechanism, instead of the conventional floating gate concept, addressing technology generations in the range of 36-28nm. The final objective of the project was to demonstrate the potential of the concept on demonstrator, realized by the industrial partners, with a target size close to the foreseen upper limit of the technology, in the order of the Gigabyte (=8 Gigabit).

The motivation of the project was coming from the increasing demand for compact memory storage from a variety of ICT applications, mainly in the field of portable devices.

During the first year of the project it appeared evident that the evolution of the standard floating gate NAND technology was going to be faster than expected, with devices in the 30-35nm generation being announced by several companies. It was therefore decided to change the overall targets of the project, putting the final objective in the 22-25nm range (comparable with the expected state-of-the-art in 2011) and anticipating a first full size demonstrator of the technology in the available 45nm generation.

CNR Principal Investigator: Sabina Spiga

Key Involved CNR researchers: Alessio Lamperti, Elena Cianci

CNR Publications:

-Francesco Driussi, Sabina Spiga, Alessio Lamperti, Gabriele Congedo, and Alberto Gambi, “Simulation study of the trapping properties of HfO2 based charge–trap memory cells”, IEEE TRANSACTIONS ON ELECTRON DEVICES61, 2056-2063 (2014)

- Sabina Spiga, Francesco Driussi, Alessio Lamperti, Gabriele Congedo, Olivier Salicio , "Effects of Thermal Treatments on the Trapping Properties of HfO2 Films for Charge Trap Memories" , Applied Physics Express 5, 021102 (2012)

-- A. Lamperti, L. Lamgna, G. Congedo, and S. Spiga, “Cubic/tetragonal phase stabilization in high-k ZrO2 thin films grown using O3-based atomic layer deposition”, J. Electrochem. Soc., Volume 158, Issue 10, pp. G221-G226 (2011)

- L . Lamagna, C. Wiemer, M. Perego, S. Spiga, J. Rodríguez, D. Santiago Coll, M.-E. Grillo, S. Klejna, S.D. Elliott, “Mechanisms for Substrate-Enhanced Growth during the Early Stages of Atomic Layer Deposition of Alumina onto Silicon Nitride Surfaces", Chemistry of Materials 24, 1080-1090 (2012)

- G. Congedo, A. Lamperti, O. Salicio, and S. Spiga, “Multi-Layered Al2O3/HfO2/SiO2/Si3N4/SiO2 Thin Dielectrics for Charge Trap Memory Applications”, ECS Journal of Solid State Science and Technology 2, p. N1-N5 (2013)

- A. Lamperti, E. Cianci, O. Salicio, L. Lamagna, S. Spiga, M. Fanciulli , "Thermal stability of high-κ oxides on SiO2/Si or SixNy/SiO2/Si for charge trapping non volatile memories" , Surface and Interface Analysis 45, 390-393 (2013)

- G. Congedo, C. Wiemer, A. Lamperti, E. Cianci, A. Molle, F. G. Volpe, and S. Spiga, “Atomic layer-deposited Al–HfO2/SiO2 bi-layers towards 3D charge trapping non-volatile memory”, Thin solid Films 533, 9 (2013),

- E. Cianci, A. Lamperti, G. Congedo and S. Spiga, “Structural and electrical properties of terbium scandate films deposited by atomic layer deposition and high temperature annealing effects” ECS Journal of Solid State Science and Technology 1, vol. 1,P5-P10 (2012)

- G. Congedo, A. Lamperti, L. Lamagna, and S. Spiga, “Stack engineering of TANOS charge-trap Flash memory cell using high-k ZrO2 grown by ALD as charge trapping layer”, Microelectronic Engineering 88, 1174 (2011).

- A. Lamperti, E. Cianci, U. Russo, S. Spiga, O. Salicio, G. Congedo, M. Fanciulli, “Synthesis and characterization of DyScO films deposited on Si and Si-rich SiN by atomic layer deposition for blocking layer replacement in TANOS stack”, J. Vac. Sci. Technol. B 29, 01AE03 (2011)

- G. Congedo, S. Spiga, U. Russo, A. Lamperti, O. Salicio, E. Cianci, M. Fanciulli, “Evaluation of DyScOx as an alternative blocking dielectric in TANOS memories with Si3N4 or Si-rich SiN charge trapping layers”, J. Vac. Sci. Technol. B 29, 01AE04 (2011)

- G. Congedo, S. Spiga, L. Lamagna, A. Lamperti, Yu. Lebedinskii, Yu. Matveyev, A. Zenkevich, P. Chernykh, M. Fanciulli, "Effect of high-temperature annealing on lanthanum aluminate thin films grown by ALD on Si(100)", Microelectronic Eng. 86, 1696-1699 (2009)